# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique Université des Sciences et de la Technologie Houari Boumediene (U.S.T.H.B) Faculé d'Electronique et d'Informatique

# Thesis

Presented in order to get the **DOCTORAT** d'Etat Diploma

In Computer Science

By

# Hadda CHERROUN

Theme

# Scheduling for High-Level Synthesis

Defended on 10 december 2007

Thesis committee

| Nadjib BADACHE         | Professor, University of Sciences and Technology<br>Houari Boumedienne, Algiers             | Chairman        |

|------------------------|---------------------------------------------------------------------------------------------|-----------------|

| Mohamed AHMED<br>NACER | Professor, LISI/ENSMA, University of Sciences<br>and Technology Houari Boumedienne, Algiers | Thesis Director |

| Paul FEAUTRIER         | Professor, LIP ENS Lyon, France                                                             | Thesis Advisor  |

| Zaia ALIMAZIGHI        | Dr., University of Sciences and Technology<br>Houari Boumedienne, Algiers                   | Examiner        |

| Mouloud KOUDIL         | Dr., National Institute in Computer Science (INI), Algiers                                  | Examiner        |

# Abstract

Scheduling is one of the important tasks in High-Level Synthesis (HLS). Scheduling a whole program, especially with loops, is hard as too many constraints and objectives interact. We propose to organize scheduling in gradual ways. This thesis focuses on some steps of the designed scheduling approaches. An efficient formalism to express resource constraints, using disequations, is presented. In the first part, we examine the problem of Resource-Constrained Scheduling (RCS) tasks whose resource usage is described by reservation tables, while in the second one, we adress the problem of RCS data-dependent tasks. For both problems, several algorithms are proposed. Our main algorithmic contributions are: 1/ an exact branch-and-bound (BAB) algorithm, where each evaluation is accelerated by variants of Floyd's and Dijkstra's algorithms, 2/ a new scheduling method based on graph coloring technique as a tool for a BAB meta-method, where each evaluation is accelerated by maximal and greedy clique computation. The evaluation and comparisons are done on pieces of real-life applications from the PerfectClub and the HLSynth95 benchmarks. The results demonstrate the suitability of these solutions for HLS scheduling.

**Keywords:** Scheduling, resource constraints, reservation tables, dis-equations, branch-andbound, Dijkstra, graph coloring, integer linear programming.

## Résumé

L'ordonnancement est l'une des tâches les plus importantes dans la synthèse de haut niveau. Vue l'importance des objectifs et des contraintes qui interagissent, il est dur d'ordonnancer, un programme en entier, en particulier lorsqu'il contient des boucles. Pour cela, nous proposons d'hiérarchiser l'ordonnancement en niveaux graduels selon différentes approches. Cette thèse se concentre sur quelques étapes de ces approches conçues. Un formalisme efficace exprimant les contraintes de ressources en utilisant les dis-équations, est présenté. Dans une première partie, nous examinons le problème de l'Ordonnancement sous Contraintes de Ressources (OCR) de tâches dont l'utilisation de ressource est décrite via des tables de réservation, tandis que dans la seconde partie, nous abordons le problème d'OCR de tâches dépendantes. Nos principales contributions sont: 1/ un algorithme exact de type Branch-and-Bound (BAB) associé à une variante de l'algorithme de Dijkstra, 2/ une nouvelle méthode d'ordonnancement basée sur la technique de coloriage de graphe et qui est résolue au moyen d' un BAB associé à un algorithme de calcul de clique (exacte/gloutonne). Les algorithmes proposés ont été implémentés. Le jeu des programmes tests est pris d'applications réelles du PerfectClub et HLSynth95 benchmarks. Les résultats prouvent que les deux méthodes conviennent aux outils HLS.

Mots-clés: Ordonnancement, contraintes de ressources, tables de réservation, dis-equations, branch-and-bound, Dijkstra, coloriage de graphe, programmation linéaire en nombres entiers.

# Acknowledgments

I would like to thank my thesis director, Professor Mohamed AHMED NACER, for his ultimate help and advices.

I would like thank also my advisor, Professor Paul FEAUTRIER, giving me the opportunity of working on this thesis in his laboratory with the members of his team, for his support and his directions. This work couldn't have been done without the advices of several other people. First, I would like to acknowledge Alain DARTE, CNRS research scientist at LIP laboratory ENS Lyon, for his ultimate help and participation in the research results.

Specially, I would like to thank Dr. AliMazighi, Professor Nadjib BADACHE first for the fact that they made a difference in my student life and for have accepted to be member of my thesis committee. Dr. Mouloud KOUDIL is also thanked to have accepted to evaluate my thesis.

Also, I would like to thank many of my friends met at the LIP laboratory whose comments helped me at the different stages of this research: Fabrice BARRY, Antoine SCHERRER, Nicolas FOURNEL, Anne BOUILLARD and Eric THIERRY.

A thesis is more than its technical contributions, it is also a personal achievement. For this, I would warmly thank my family and friends. First, my husband Mouloud who joined me in this adventure. Thank you for your loving trust and your support. I would also like to thank my family: my mother for her loving and ultimate help and support, my brothers and sisters whose encouragements throughout my studies have always been the greatest help.

This is also a good opportunity to thank some of the people who really made a difference in my student life. K. REGHI and B. CHATTA professors at Benammer Collége and A. BENGUIT at Hadj Aissa Lycée and most of my teachers at the USTHB university especially N. BENSAOU and N. MADANI.

Finally, my deepest gratitude goes to my close friends Attika, Badra, Hayet, Malika, Mounira, and Zineb. Their friendship and love have helped me a lot and their acknowledgment cannot be expressed by words.

To Allah

To Mouloud To my Mother

# Table of Contents

| List o | f Fig | ures                                                           | viii |

|--------|-------|----------------------------------------------------------------|------|

| List o | f Tab | bles                                                           | ix   |

| 1      | Intr  | oduction                                                       | 1    |

|        | 1.1   | Synthesis and High-Level Synthesis                             | 2    |

|        |       | 1.1.1 Partitioning                                             | 3    |

|        |       | 1.1.2 Scheduling                                               | 3    |

|        |       | 1.1.3 Allocation - Binding-                                    | 4    |

|        | 1.2   | Objectives, Constraints & Peculiarities when Scheduling in HLS | 4    |

|        |       | 1.2.1 Constraints                                              | 4    |

|        |       | 1.2.1.1 Precedence/Control Constraints                         | 4    |

|        |       | 1.2.1.2 Resource Constraints -Sharing Resources                | 5    |

|        |       | 1.2.1.3 Time Constraints                                       | 5    |

|        |       | 1.2.1.4 Special Constraints                                    | 5    |

|        |       | 1.2.2 Datapath Peculiarities                                   | 5    |

|        |       | 1.2.3 Interaction with Allocation                              | 6    |

|        | 1.3   | Context                                                        | 6    |

|        | 1.4   | Scheduling Problems Addressed                                  | 8    |

|        | 1.5   | Objectives                                                     | 9    |

|        | 1.6   | Contributions                                                  | 9    |

|        | 1.7   | Thesis' Overview                                               | 10   |

| 2      | Stat  | e of the Art                                                   | 11   |

|        | 2.1   | Internal Representation and Constraints Formalisms             | 11   |

|        |       | 2.1.1 Internal Representation Formalisms                       | 11   |

|        |       | 2.1.2 Constraints Formalisms                                   | 12   |

|        | 2.2   | Scheduling Strategies                                          | 13   |

|        |       | 2.2.1 Basic Algorithms                                         | 14   |

|        |       | 2.2.1.1 ASAP                                                   | 14   |

|        |       | 2.2.1.2 ALAP                                                   | 15   |

|        |       | 2.2.2 Critical Path Method                                     | 15   |

|        |       | 2.2.3 List-scheduling                                          | 15   |

|        |       | 2.2.4 Force-Directed Scheduling (FDS)                          | 16   |

|   |                                           | 2.2.5                                                                                                        | Path-Based Scheduling                       | 17                                                        |

|---|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|

|   |                                           | 2.2.6                                                                                                        | Exact Algorithms                            | 18                                                        |

|   |                                           |                                                                                                              | 2.2.6.1 Integer Linear Programming          | 18                                                        |

|   |                                           |                                                                                                              | 2.2.6.2 Constraint Programming Technique    | 20                                                        |

|   |                                           | 2.2.7                                                                                                        | Miscellaneous Techniques                    | 21                                                        |

|   |                                           |                                                                                                              | 2.2.7.1 Simulated Annealing Based Algorithm | 21                                                        |

|   |                                           |                                                                                                              | 2.2.7.2 Genetic Algorithm                   | 22                                                        |

|   | 2.3                                       | High-L                                                                                                       | level Synthesis Tools                       | 22                                                        |

|   |                                           | 2.3.1                                                                                                        | GAUT                                        | 23                                                        |

|   |                                           | 2.3.2                                                                                                        | SPARK                                       | 23                                                        |

|   |                                           | 2.3.3                                                                                                        | Ugh                                         | 25                                                        |

|   |                                           | 2.3.4                                                                                                        | MMAlpha                                     | 26                                                        |

|   | 2.4                                       | Schedu                                                                                                       | lling using Reservation Tables              | 27                                                        |

|   |                                           |                                                                                                              |                                             |                                                           |

|   | 2.5                                       | Hierard                                                                                                      | chical basis Scheduling Frameworks          | 27                                                        |

|   | $\begin{array}{c} 2.5 \\ 2.6 \end{array}$ |                                                                                                              |                                             | 27<br>28                                                  |

| 3 | 2.6                                       | Conclu                                                                                                       | usion                                       |                                                           |

| 3 | 2.6                                       | Conclu<br>eral So                                                                                            | cheduling Approaches                        | 28                                                        |

| 3 | 2.6<br>Gen                                | Conclu<br>eral So                                                                                            | rsion                                       | 28<br><b>29</b>                                           |

| 3 | 2.6<br>Gen                                | Conclu<br>eral So<br>Syntol                                                                                  | usion                                       | 28<br><b>29</b><br>29                                     |

| 3 | 2.6<br>Gen                                | Conclu<br>eral So<br>Syntol<br>3.1.1<br>3.1.2                                                                | usion                                       | 28<br><b>29</b><br>29<br>29                               |

| 3 | 2.6<br>Gen<br>3.1                         | Conclu<br>eral So<br>Syntol<br>3.1.1<br>3.1.2<br>A Sche                                                      | usion                                       | 28<br><b>29</b><br>29<br>29<br>32                         |

| 3 | 2.6<br>Gen<br>3.1<br>3.2                  | Conclu<br>eral So<br>Syntol<br>3.1.1<br>3.1.2<br>A Sche<br>Stepwi                                            | usion                                       | 28<br><b>29</b><br>29<br>32<br>33                         |

| 3 | 2.6<br>Gen<br>3.1<br>3.2                  | Conclu<br>eral So<br>Syntol<br>3.1.1<br>3.1.2<br>A Sche<br>Stepwi                                            | usion                                       | 28<br><b>29</b><br>29<br>32<br>33<br>33                   |

| 3 | 2.6<br>Gen<br>3.1<br>3.2                  | Conclu<br>eral So<br><i>Syntol</i><br>3.1.1<br>3.1.2<br>A Sche<br>Stepwi<br>3.3.1<br>3.3.2                   | usion                                       | 28<br>29<br>29<br>32<br>33<br>33<br>34                    |

| 3 | 2.6<br>Gen<br>3.1<br>3.2<br>3.3           | Conclu<br>seral So<br>Syntol<br>3.1.1<br>3.1.2<br>A Sche<br>Stepwi<br>3.3.1<br>3.3.2<br>Compi                | usion                                       | 28<br>29<br>29<br>32<br>33<br>33<br>34<br>35              |

| 3 | 2.6<br>Gen<br>3.1<br>3.2<br>3.3<br>3.4    | Conclu<br>eral So<br>Syntol<br>3.1.1<br>3.1.2<br>A Sche<br>Stepwi<br>3.3.1<br>3.3.2<br>Compi<br><i>CLooG</i> | usion                                       | 28<br><b>29</b><br>29<br>32<br>33<br>33<br>34<br>35<br>37 |

Part I Reservation Tables Scheduling using Dis-equations

| 4 | Formalism and a Greedy Solution |                                                                                                                                               |   |  |  |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

|   | 4.1                             | Introduction                                                                                                                                  | 5 |  |  |

|   | 4.2                             | Task and Resource Constraints Formalism    43                                                                                                 | 5 |  |  |

|   |                                 | 4.2.1 Extracting Tasks with Reservation Tables                                                                                                | 5 |  |  |

|   |                                 | 4.2.2 Notations                                                                                                                               | 6 |  |  |

|   |                                 | 4.2.3 Forbidden Distances $\dots \dots \dots$ | 6 |  |  |

|   |                                 | 4.2.4 Example 1                                                                                                                               | 7 |  |  |

|   | 4.3                             | Scheduling Problem Formulation                                                                                                                | 8 |  |  |

\_

|          | 4.4                      | How To solve a System of Dis-equation?                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                     | 8                                                                                                                                                                         |

|----------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.5                      | A Greedy Heuristic                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                     | 9                                                                                                                                                                         |

|          |                          | $4.5.1  Algorithm  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                                                                                                                                                                                                                                                                                                                                                            | 4                                                     | 9                                                                                                                                                                         |

|          |                          | 4.5.2 Example 1, Continued                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                     | 0                                                                                                                                                                         |

|          |                          | 4.5.3 Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                     | 1                                                                                                                                                                         |

|          | 4.6                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                     | 2                                                                                                                                                                         |

| <b>5</b> | Inte                     | ger Linear Programming Approach                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                     | 3                                                                                                                                                                         |

|          | 5.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                     | 3                                                                                                                                                                         |

|          | 5.2                      | Integer Linear Programming Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                     | 5                                                                                                                                                                         |

|          |                          | 5.2.1 Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                     | 6                                                                                                                                                                         |

|          |                          | 5.2.2 Standard $0/1$ Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                     | 6                                                                                                                                                                         |

|          |                          | 5.2.3 $0/1$ Simplified Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                     | 6                                                                                                                                                                         |

|          |                          | 5.2.4 Big-M Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                     | 7                                                                                                                                                                         |

|          |                          | 5.2.5 Experiments $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                               | 5                                                     | 8                                                                                                                                                                         |

|          | 5.3                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                     | 9                                                                                                                                                                         |

| 6        | Bra                      | nch-and-Bound-Based Longest-Path Computation Solution                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                     | 0                                                                                                                                                                         |

|          |                          | non-and-Dound-Dased Dongest-1 and Computation Solution                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                       |                                                                                                                                                                           |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                     | -                                                                                                                                                                         |

|          |                          | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                     | 0                                                                                                                                                                         |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · · · 6                                               | 0                                                                                                                                                                         |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · · · 6<br>· · · 6<br>· · · 6                         | 0<br>1<br>2                                                                                                                                                               |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · · · 6<br>· · · 6<br>· · · 6<br>· · 6                | $0 \\ 1 \\ 2 \\ 3$                                                                                                                                                        |

|          | 6.1                      | General Introduction       An Exact Branch-and-Bound Solution         6.2.1       Finding the Local Bound         6.2.1.1       Floyd-based Algorithm                                                                                                                                                                                                                                                                                                                   | · · · · 6<br>· · · 6<br>· · · 6<br>· · · 6<br>· · · 6 | $0 \\ 1 \\ 2 \\ 3 \\ 4$                                                                                                                                                   |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6<br>6<br>6<br>6<br>6<br>6                            | 0<br>1<br>2<br>3<br>4<br>6                                                                                                                                                |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6<br>6<br>6<br>6<br>6<br>6<br>6                       | 0<br>1<br>2<br>3<br>4<br>6<br>6                                                                                                                                           |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | 0<br>1<br>2<br>3<br>4<br>6<br>8                                                                                                                                           |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | 0<br>1<br>2<br>3<br>4<br>6<br>8<br>8                                                                                                                                      |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | 0<br>1<br>2<br>3<br>4<br>6<br>8<br>8<br>8                                                                                                                                 |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | 0<br>1<br>2<br>3<br>4<br>6<br>8<br>8<br>8<br>9                                                                                                                            |

|          | 6.1                      | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | $     \begin{array}{c}       0 \\       1 \\       2 \\       3 \\       4 \\       6 \\       8 \\       8 \\       9 \\       9 \\       9 \\       9     \end{array} $ |

| 7        | 6.1<br>6.2<br>6.3        | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | $     \begin{array}{c}       0 \\       1 \\       2 \\       3 \\       4 \\       6 \\       8 \\       8 \\       9 \\       9 \\       2 \\       2     \end{array} $ |

| 7        | 6.1<br>6.2<br>6.3        | General Introduction       An Exact Branch-and-Bound Solution         6.2.1       Finding the Local Bound         6.2.1.1       Floyd-based Algorithm         6.2.1.2       Dijkstra-based Incremental Algorithm         6.2.2       Complexity         6.2.3       Speeding up the BAB Algorithm         6.2.3.1       Heuristic 1         6.2.3.2       Heuristic 2         6.2.3.3       Heuristic 3         6.2.4       Experiments         6.2.4       Experiments |                                                       | 0<br>1<br>2<br>3<br>4<br>6<br>8<br>8<br>9<br>9<br>2<br><b>3</b>                                                                                                           |

| 7        | 6.1<br>6.2<br>6.3<br>Con | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | 0<br>1<br>2<br>3<br>4<br>6<br>8<br>8<br>8<br>9<br>9<br>2<br><b>3</b><br>3                                                                                                 |

# Part II Resource-Constrained Scheduling using Graph Coloring

| 8 Scheduling via Branch-and-Bound-Based Graph Coloring |                |    |  |  |  |  |

|--------------------------------------------------------|----------------|----|--|--|--|--|

|                                                        | 8.1 Formalisms | 78 |  |  |  |  |

\_

\_

|              |      | 8.1.1 Task Model                                          | 78 |

|--------------|------|-----------------------------------------------------------|----|

|              |      | 8.1.2 Data Dependences and Resource Constraints Formalism | 79 |

|              | 8.2  | Scheduling Problem Formulation                            | 80 |

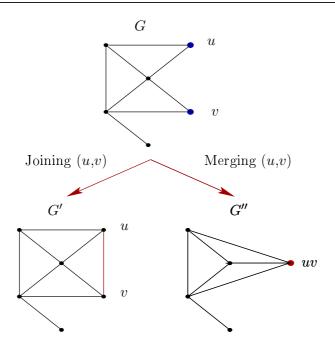

|              | 8.3  | How To Color a Graph?                                     | 81 |

|              | 8.4  | Branch-and-Bound-Based Graph Coloring Solution            | 83 |

|              |      | 8.4.1 Branching Rule                                      | 83 |

|              |      | 8.4.2 Evaluation -Bounding- Procedure                     | 83 |

|              |      | 8.4.3 Algorithm                                           | 86 |

|              |      | 8.4.4 Complexity                                          | 87 |

|              | 8.5  | Integer Linear Program Solution                           | 87 |

|              | 8.6  | Experimental Results and Discussion                       | 88 |

|              | 8.7  | Conclusion                                                | 88 |

| 9            | Gen  | eral Conclusion and Future Directions                     | 90 |

|              | 9.1  | Contribution                                              | 90 |

|              | 9.2  | Future Directions                                         | 91 |

| Glossa       | ary  | (                                                         | 94 |

| Biblio       | grap | hy                                                        | 97 |

| $\mathbf{A}$ | Gra  | ph Algorithms 10                                          | 05 |

|              | A.1  | Depth-First Search Algorithm and its Features             | 05 |

|              | A.2  | Maximal-weight Paths                                      | 07 |

|              |      | A.2.1 Relaxation Technique                                | 07 |

|              |      | A.2.2 Dijkstra's Algorithm                                | 08 |

|              |      | A.2.3 Bellman-Ford's Algorithm                            | 09 |

|              |      | A.2.4 Floyd-Warshall's Algorithm                          | 09 |

|              |      | A.2.5 Johnson's Algorithm                                 | 10 |

|              | A.3  | Roy-Warshall's Algorithm                                  | 11 |

| В            | Ben  | chmark Description 11                                     | 14 |

|              | B.1  | 1995' High-Level Synthesis Design Repository              | 14 |

|              |      |                                                           |    |

# List of Figures

| 1.1 | The Hierarchical Scheduling Views                       |

|-----|---------------------------------------------------------|

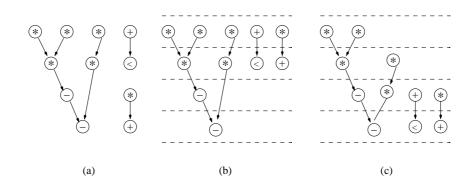

| 2.1 | (a) Data Flow Graph (b) ASAP Schedule (c) ALAP Schedule |

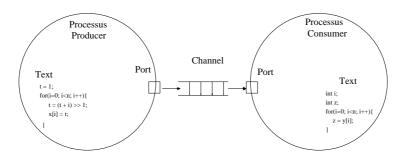

| 3.1 | Pipeline System                                         |

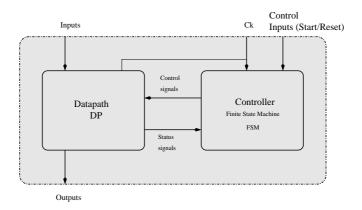

| 3.2 | Target of HLS - RTL processor                           |

| 3.3 | The Hierarchical Scheduling Views                       |

| 3.4 | Design Flow of our HLS System                           |

| 3.5 | Generated FSM for the Pipeline Program                  |

| 4.1 | Forbidden Distance                                      |

| 4.2 | Binding for Example 1                                   |

| 4.3 | (a) Greedy Solution and (b) Optimal Solution            |

| 5.1 | Feasible Areas.                                         |

| 6.1 | Pathological Case css21                                 |

| 8.1 | One unit-cycle resource simulation                      |

| 8.2 | Binding for the Example                                 |

| 8.3 | The Graphs $G, G'$ and $G''$ . 84                       |

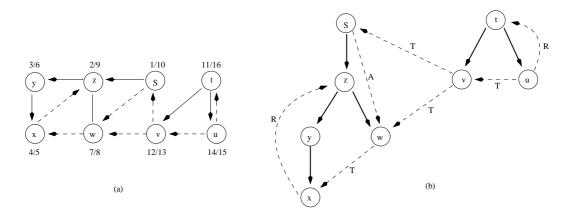

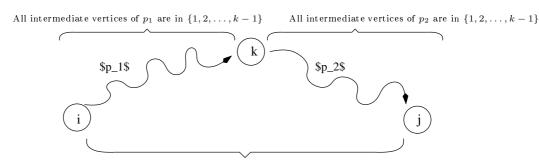

| A.1 | DFS Properties                                          |

# List of Tables

| 4.1                                              | Greedy Scheduling Results.                                                                                                                                                                                                                                      | 51                   |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 5.1                                              | Scheduling Results with the Different ILP Formulations.                                                                                                                                                                                                         | 59                   |

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \end{array}$ | Scheduling Results for the Various Tests on the BAB Algorithms. $\ldots$ $\ldots$ Improvements on the BAB Algorithm with $L_{\text{best}}$ Set to the GS Schedule Latency. Influence of the Binding Heuristic on Latency and Resolution Time. $\ldots$ $\ldots$ | 70<br>71<br>71       |

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4$                       | Comparative Results.Comparative Results when the $p_i$ Vary.Comparative Results when the $p_i$ Vary.Comparative Results with Artificial Data Dependances.Comparative Results when Splitting a few Macro-tasks.                                                  | 74<br>74<br>75<br>75 |

| 8.1                                              | Scheduling Results for the BAB with both Maximal and Greedy Clique Bounding Algorithms and the ILP.                                                                                                                                                             | 89                   |

| A.1                                              | Summary of Longest-Paths Algorithms.                                                                                                                                                                                                                            | 112                  |

| B.1<br>B.2                                       | Features of Designs                                                                                                                                                                                                                                             |                      |

# Chapter 1

# Introduction

In this thesis, the *resource-constrained scheduling problem* in High-Level Synthesis -behavioral synthesis- will be examined, and several algorithms are proposed. The aim of this research is to propose and compare some novel scheduling algorithms, as well from theoretical point of view as experimental one. These algorithms are integrated in *stepwise scheduling approaches*.

With the rise in the complexity of Integrated Circuits (IC's), their design process has become very difficult to manage without any automation or semi-automation. Thus the need of effective and good CAD tools where we can have: shorter design cycle, fewer errors, the ability to search the design space, documenting the design process and availability of digital circuit technology to more people. The challenge of embedded system design is twofold: one must pack computeintensive algorithms in small platforms; furthermore, the design must be completed as fast as possible, to meet the demands of a highly volatile market. In the long run, this will be possible only if computer-aided design tools are developed far beyond their present status [24].

An artifact such as a cell phone or a digital TV set must behave according to given specifications; however, its hardware parts can only be built from a structural description. The goal of High-Level Synthesis (HLS) is to convert a *behavioral specification* – for the whole or a part of the complete application, to be performed on a dedicated circuit – into a *structural description*, while optimizing several objective functions: performance, size, power consumption among others.

In the past two decades [34] there has been a lot of activity going on in the area of High-Level synthesis and it is becoming an increasingly popular research topic. Currently, several commercial [103, 78, 102] and academic HLS [49, 77, 88, 71, 55, 37] tools exist but the design community don't integrate them into its design flow, because of many reasons: they lack interaction between them and the designers, they can support only limited architectures and the quality of the design they generate is still often worse than that of manual design.

Our contribution focuses on the scheduling problem as it is one key process in HLS. Our aim is to improve those tools by reusing some of methods and models that have been pioneered by the compiler community. Among these powerful methods, operations research techniques have strongly increased the performances of scheduling task.

Scheduling is an important and primary task in HLS. However, scheduling operations under resource constraints to minimize the total duration is  $\mathcal{NP}$ -complete problem as too many constraints and objectives interact [104, 26]. For efficiently scheduling programs, especially with loops, first, we facilitate the problem by this trick. We propose to organize the scheduling process in **stepwise ways**.

The purpose of these hierarchical decompositions is twofold: one can integrate exact methods into these hierarchical scheduling approaches, that could identify code fragments and schedule them optimally such that it couldn't affect a lot the whole scheduling quality; furthermore, it allows to avoid dealing with a too large system as is well known, applying linear programming to large constraint systems is not cost-effective.

In what follow, we will present briefly the area, the context and the objectives of this research. After what, we report the main contributions. We conclude by giving the outline of the thesis.

# 1.1 Synthesis and High-Level Synthesis

The High-Level -architectural or behavioral- Synthesis (HLS) process takes a behavioral specification of a system and a set of constraints and goals to be satisfied, and finds a structure that implements the behavior while satisfying the goals and constraints [34]. These goals and constraints can express several objective functions: performance, size, power consumption...

Some times called "hardware compilation", the synthesis of circuits translates a sequential program, into an integrated circuit (hardware). The aim of the synthesis tool is to obtain the physical view of the circuit. This view can be represented by a netlist which is a structural view in the logic-gates level. However, there are several lower-level tools - logic synthesis- which allow the translation to this structural view: Synopsys [103], Cadence [22], Catapult [78], ISE Xilinx tools [113]. Most of them start working on Register Transfer description Level (RTL). Indeed, at the RTL level, the input description is transformed in such way that the register assignation and the functional units assignation are fixed for each cycle of the system [34]. We are interested by the part of the HLS which fills the gap between system " behavioral" level and the RT level by automatically generating an RTL realization from a behavioral description.

#### Generic High-Level Synthesis System

A typical way of describing behavior is to write a program in an ordinary computer language or in a special hardware description language such as VHDL [29] or Verilog [98].

The first step in HLS is usually the compilation of the behavioral description into an internal representation that is most suitable for HLS tasks. Most approaches use graph-based representations that gather both data flow and control flow implied by the specification. These internal representations are given different names in different synthesis systems (e.g. value trace, data dependency graph [3], directed acyclic graph, control and data flow graphs(CDFG) [49]) but are simply different adaptations of similar basic concepts. CDFG is the most popular and in many systems, the control flow graph and the data flow graph are integrated into one structure. Control dependences are derived directly from the explicit order given in the input program and from the compiler's choices of parsing the arithmetic/logic expressions. Data dependences show the essential ordering of operations.

At this stage and like in the software compilation, some important tasks and some optimizations should be performed by the compiler. They include variable disambiguation, taking care of the scope of variables, converting complex data structures into simple types, type checking, expression simplification, dead code elimination, constant propagation, common subexpression elimination....

The second step of the HLS, which is the core of transforming behavior into structure, includes four major tasks:

• *Partitioning:* deals with the division of the intermediate representation (i.e. the behavioral description or the design) into sub-representations in order to reduce the problem size and exhibit more parallelism.

- *Scheduling:* partitions the intermediate representation into time steps, thereby generating a finite-state machine model.

- Allocation: though closely intertwined with scheduling, involves partitioning the intermediate representation with respect to space (hardware resources) which is also known as spatial mapping.

- Control generation: Once the schedule and allocation have been computed, it is necessary to synthesis a controller (hardwired or microcoded) that will drive allocated resources as required by the schedule. Finally, the design has to be converted into real hardware. Lower level tools, such as logic synthesis and layout synthesis, complete the design.

#### 1.1.1 Partitioning

Software programming languages have little support for describing hardware efficiently. For example, to model hardware in C/C++, we need additional language features present in Hardware Description Language (HDL) but not present in C/C++:

- Concurrency : hardware is inherently parallel, while C/C++ programs and the like are inherently sequential. The notion of processes (*Always* blocks in Verilog HDL, *Process* in VHDL), which encapsulates programs that execute concurrently, have to be introduced. A system will be described as a network of processes.

- Signals : hardware processes need to use signals (akin to wires or buffered channels) to communicate with one another.

- Reactivity : hardware systems are in continuous interaction with heir environment, i.e. they are reactive. The notion of reactivity is essential to describing hardware systems at all levels of abstraction.

- Data abstraction : C/C++ supports data abstractions that are useful for software programming. However, for hardware, one needs arbitrary precision signed and unsigned integers, bit vectors and fixed point types.

With such a set of features added, an imperative language, like C/C++, can efficiently model hardware/software systems. Thus the aim of partitioning is to transform the input description such that it will be easily and efficiently described in HDL.

### 1.1.2 Scheduling

A Finite State Machine with Datapath (FSMD) model is the most popular one which is used to describe digital systems at the RT level [44]. It consists of an FSM called the control unit and a datapath. The datapath consists of the storage and functional units necessary for the system. The FSM consists of a set of states, a set of transitions between states, and a set of actions (involving the datapath) associated with each transition.

Scheduling, an important task in HLS, can be described as the process of dividing the intermediate representation into states and control steps, in such a way that can be directly synthesized into an FSMD model. In other words, scheduling does a temporal mapping of the given representation. A behavioral description and hence the intermediate representation consists of a sequence of operations to be performed by the synthesized hardware. The task of scheduling partitions these operations into time steps such that each operation is executed in one time step. Each time step corresponds to one state of the controlling FSM state machine in the FSMD model.

# 1.1.3 Allocation -Binding-

The binding task assigns the functional operations and memory accesses to available hardware units. A resource such as a functional, storage, or interconnection unit can be shared by different operations, data accesses, or data transfers if they are mutually exclusive. Binding consists of three subtasks based on the unit type:

- Storage binding assigns variables to storage units. Storage units can be of many types, including registers, registers files, and memory units. Two variables that are not alive simultaneously in a given state can be assigned to the same register. Two variables that are not accessed simultaneously in a given state can be assigned to the same port or a register file or memory.

- *Functional-unit binding* assigns each operation to a functional unit. A functional unit or a pipeline stage can execute only one operation per clock cycle.

- *Interconnection binding* assigns an interconnection unit such as a multiplexer, a wire or a bus for each data transfer among ports, functional units, and storage units.

# 1.2 Objectives, Constraints & Peculiarities when Scheduling in HLS

Scheduling, a central task in HLS, involves determining the execution order of operations in a behavioral description. In other words, it is the process of determining the assignment of operations to time slots (control steps) of a synchronous system subject to various constraints.

# 1.2.1 Constraints

The scheduling problem in HLS must take into account different and heterogeneous constraints, which define requirements imposed on an implementation of a system. There are at least two kinds of constraints. The first group, as in classic scheduling problems, comprises constraints that can be **deduced from a system behavioral description**, such as precedence constraints -*data dependences*-, or conditions for operation execution -*control dependences*-. The other group of constraints defines non-functional **requirements for possible implementations** of the system such as *performance*, *cost*, *timing*, *power consumption* or *memory requirements*.

# 1.2.1.1 Precedence/Control Constraints

Two types of dependencies exist between the operations from a program specification. Dataflow dependencies impose precedence (execution order) between the operations. For example, operation  $o_2$  has to be executed after operation  $o_1$ , if a result computed by  $o_1$  is used by  $o_2$ . Control-flow dependencies arise when some portions of the specification are executed conditionally. All data-flow and control-flow dependencies have to be satisfied to ensure a correct execution of the specified behavior.

## 1.2.1.2 Resource Constraints -Sharing Resources-

Additional constraints arise due to finite hardware resources. Resource constraints impose bounds on a number of functional units available for the task execution. For example, a system implementation may incorporate two adder circuits and, consequently, not more than two additions can be executed simultaneously.

### 1.2.1.3 Time Constraints

Another set of restrictions comes from the timing constraints. In many critical applications e.g. aircraft engine control, computer hardware has to react to a recognition of a specific event within a strictly prescribed time interval.

## 1.2.1.4 Special Constraints

The resource-constrained scheduling can consider resources very broadly and therefore power consumption and area can also be defined as a resource. In this thesis we don't explicitly address this kind of constraints.

# 1.2.2 Datapath Peculiarities

Additionally to this panoply of constraints, scheduling in HLS can not be treated without actually considering realistic design models that would have special resources. Indeed the resources usually have some features like functional units with varying delays and multi-functional units. These issues are not explicitly addressed by our main contribution so just to provide to the reader a global idea, we discuss them briefly:

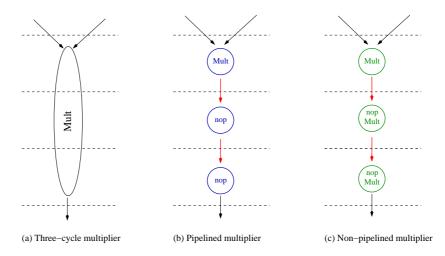

- Functional units with varying delays: each functional unit will have a different delay and therefore it assumes that an operation assigned to a control step would take the same time as another operation. This assumption would lead to a clock cycle that is unusually lengthened by the slowest unit in the design. The following three approaches are used to solve this problem:

- *Pipelining*: A functional unit may have stages in it. This makes it possible to execute two operations in the same functional unit since they operate in two different stages. As known, pipelining is a simple technique to increase parallelism.

- Multi-cycling: If the clock cycle is shortened to allow fast operation, then the slower operation would take multiple clocks and hence are called multi-cycle operations. However input latches are needed in front of the multi-cycle functional units to hold its operands until its results are available. This would in turn increase the size of the control logic. Multi-cycle operations can be pipelined.

- Chaining: Two or more operations could be allowed to be performed sequentially in a single control step (same clock cycle). Since the output of one functional unit has to be fed to another, they should be directly connected.

- **Multi-functional Units:** it has been assumed that a functional unit can perform only one operation but in practice there are several cost effective multi-functional units being used. For this purpose the scheduling algorithms could be technology based so that it can explore the library of components. For example, an operation in the critical path could be assigned faster functional units than those not in the critical path. Also the scheduling algorithm

could try to use the same multi-functional unit for two data independant operations which are in two different steps.

#### **1.2.3** Interaction with Allocation

In order to know whether two operations can be scheduled in the same control step, one must know whether they use common resources. Moreover, finding the most efficient schedule, for real hardware, requires knowing the delays for the different operations, however those can only be found after that the details of the function units and their interconnections are known. On the other hand, in order to make a good allocation, one must know what operations will be done in parallel, which comes from the schedule. Therefore, scheduling and allocation are **strongly interdependent** tasks.

In the literature, many scenarios have been explored. The most straightforward approach to this problem is to set some limits on the resources cost and then schedule, as it is done in many systems. A more flexible approach is to iterate the whole process changing the resource limits until a satisfactory design has been found. An exact approach, but an expensive one, is to develop the schedule and allocation simultaneously, as in system MAHA [88]. Finally, the allocation can be done first, followed by scheduling as it is done in the BUD system [77].

# 1.3 Context

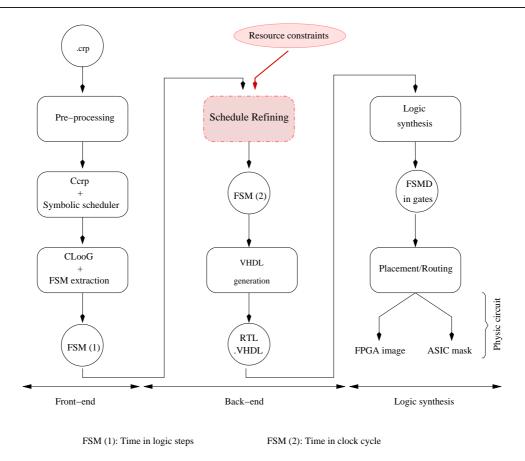

The schedulers we describe in this thesis are part of our HLS tool, we currently develop, whose aim is HLS in the field of compute-intensive embedded systems. The input specification is a variant of C (including loops); the output is a hardware description at the RT level. We use the finite state machine with a data path (FSMD) model to describe the hardware at this level.

Scheduling is the basic tool we use for hardware generation: a schedule is a precise description of the operations to be executed at each clock cycle; thus deducing the FSMD from a schedule is considered as a natural task.

Earlier work starts by building the control and data flow graph (CDFG), which is simply the sequential flow diagram of the input description. The nodes of the CDFG are the basic blocks of the original program. Most synthesis tools exploit only parallelism inside basic blocks; the FSMD is usually obtained by scheduling the tasks of each basic block of the CDFG independently. Some parallelism is exploited in loops, but mostly through loop unrolling. Our approach is quite different because we first construct a FSMD from an equivalent parallel code that exhibits the inherent parallelism in the input description and takes into account the imperfect loop nests. Afterwards, according to the resource constraints, we exploit a part or all of this parallelism.

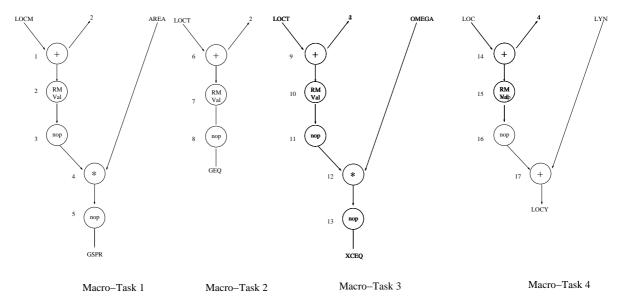

Indeed, to extract parallelism from the loops of the input description, we use a scheduling strategy previously used for automatic loop parallelization [41]. This technique which has already proved it efficiency, assigns a symbolic "date" to each **high-level statement** of the program i.e., each statement in the C program and allows us to rewrite the code into a form with explicit parallelism. This technique will be detailed in Chapter 3. The result of this scheduling pass is the definition of a sequence of *fronts*, i.e., a sequence of logical steps where each step (a front) is a group of macro-tasks to be executed in this logical step. From this result, we build a first coarse FSMD; coarse as the time is measured in logical steps instead of clock cycle. Thus, each state contains a set of data independent macro-tasks and each of them is composed by a sequence of elementary operations. However, this symbolic scheduling technique is quite complex and cannot take into account all the micro-operations (and the architectural resources they need) that are

implied in the execution of one macro-task. This fact lead us to design **stepwise scheduling approaches** to schedule programs, with loops, down to RTL.

Many factors and reasons let us to think that such approaches can improve a lot the performance of the scheduling algorithm in term of compromise quality of the schedule and its runtime. Indeed, let us notice that the application size, the diverse nature of constraints, all peculiarities of the datapath - features of the resources- and the requirements of a possible implementation can not be taken into account into one pass to get *an optimal* or *suboptimal* schedule without exploding. In Chapter 3, we will explain in details the motivations that lead us to this choice.

Now, we must refine this schedule by "splitting this logical step into elementary steps such that resource constraints and all peculiarities of the datapath will be respected". Time will be measured in physical time i.e., clock cycle of the target architecture. How to perform this? In this thesis, we have sketched and investigated two hierarchical scheduling approaches.

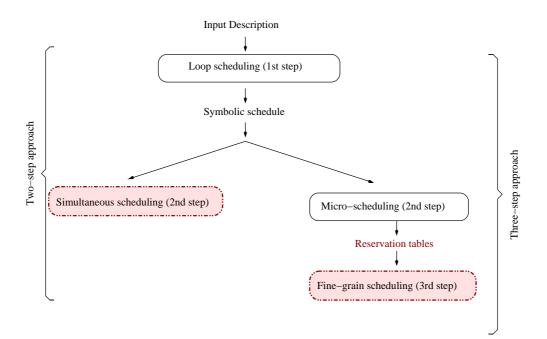

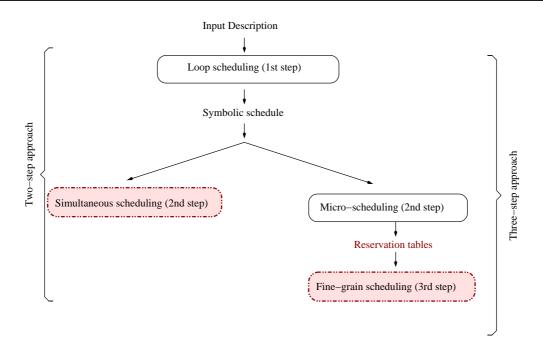

1. Two-step Approach:

After the previous symbolic scheduling step, one natural possibility is to consider, for scheduling under resource constraints, all the micro-operations of a front simultaneously. In other words, schedule them at the same time while considering resource constraints. We call this last step *simultaneous scheduling*.

2. Three-step Approach:

Again for complexity reasons one can alternatively consider another possibility. Indeed, we consider that, in our context, it will be good enough to decouple the problem in two subproblems. This partitioning can be sketched as:

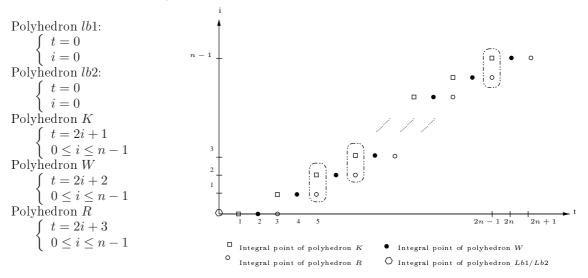

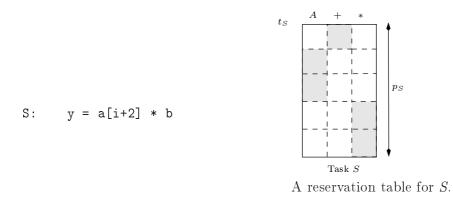

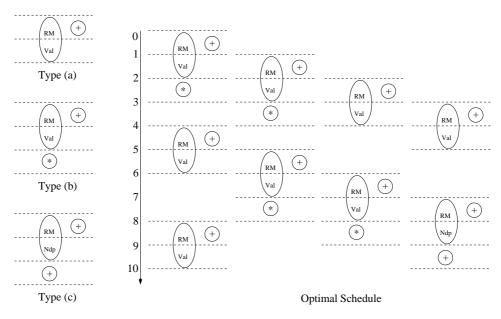

- After the symbolic scheduling, we first schedule each macro-task *independently*, taking into account all peculiarities of the data path. The schedule of each macro-task will be summarized with a *reservation table*<sup>1</sup> that states which resources at which cycle (relative to the starting time of the macro-task) are used by this macro-task. We call this second step *micro-scheduling*.

- Due to our particular construction, the macro-tasks, represented now by reservation tables, in a front are data independent but they may still interfere in their use of resources. The logical step must then be split into as few elementary steps as necessary to satisfy detailed resource constraints. We call this third step *fine-grain scheduling*.

The strengths and weaknesses of each solution, as a scheduling approach, are reported and discussed. For instance, one could emphasize that it would be better to consider, the first approach in which the micro- and fine-grain scheduling are performed at the same time. Even though, we have investigated both approaches, the last decoupling will be good enough. it is difficult to prevent the scheduler to introduce delays between micro-operations, and hence to imply more registers for holding temporary results. Our second approach may be sub-optimal, but we believe that the possible improvements do not warrant the added complexity.

Figure 3.3 summarizes both scheduling decompositions. Dotted lines expresses the area of our main contributions as in this thesis we have focused on some levels of these designed gradual scheduling approaches by suggesting mainly two solutions to the resource-constrained scheduling problems defined by the "fine-grain" and the " simultaneous" scheduling steps. Before that, we propose a new formalism for expressing resource constraints using dis-equations.

<sup>&</sup>lt;sup>1</sup>A reservation table is a matrix that shows the corresponding assignment between control cycles and resource occupation. The rows of a reservation table correspond to control cycles, the columns to resources.

Figure 1.1: The Hierarchical Scheduling Views

# 1.4 Scheduling Problems Addressed

Scheduling takes many forms, such as job-shop scheduling, production scheduling, multiprocessor scheduling and so on. To be more precise when defining our scheduling problems, let us recall that scheduling can be of several kinds:

- *Static scheduling*: All information are available to the scheduling algorithm, which runs before any real computation starts. These algorithms are called offline algorithms.

- *Semi-static scheduling:* Information may be known at program startup, or at the beginning of each time step, or at other well-defined points.

- Dynamic scheduling: Information aren't known until mid-execution as in real-time systems. These algorithms are called online ones.

In general, solving static scheduling problems under resource constraints is  $\mathcal{NP}$ -hard. This involves assigning the vertices (tasks) of an acyclic directed graph onto a set of resources, such that the total time to process all the tasks is minimized. The total time to process all the tasks is usually referred to as the makespan or latency.

An additional objective is often to achieve a short latency while minimizing the use of resources. Such multi-objective optimization problems involve complex trade-offs and compromises, and good scheduling strategies are based on a detailed and deep understanding of the specific problem domain.

As defined in our context due to our particular construction, at the fine-grain scheduling step (resp. the simultaneous scheduling), all information about the macro-tasks (resp. operations) in a front are known before scheduling. Thus, we deal with *static* and *acyclic resource-constrained* scheduling problems. They are static as they are done at compilation time and all informations are available, and acyclic as each front is a sequence of data/control independant macro-tasks without loop.

Now, we summarize in these definitions both scheduling problems addressed in this thesis:

**Definition 1.** Fine-grain scheduling: is the process of determining the optimal assignment of macro-tasks, defined by reservation tables, to time steps on a synchronous system, subject to resource constraints.

**Definition 2.** Simultaneous scheduling: is the process of determining the optimal assignment of operations to time steps on a synchronous system, subject to data dependences and resource constraints.

# 1.5 Objectives

In this thesis, the scheduling approaches, that we have designed and their corresponding techniques which are developed to solve part of scheduling levels have multiple objectives:

- Exploit efficiently more parallelism in the whole program particularly within nested loops; by efficiently partitioning the input description and applying some techniques that have proven their efficiency in automatic parallelization;

- Deal with the constraints into higher levels in the HLS design process where a global view is more clear than in lower levels;

- Formally and uniformly express constraints (data dependence and resource constraints);

- Bring some guarantee on the quality of the computed schedules;

- As the defined problems are  $\mathcal{NP}$ -hard, try to integrate exact methods into hierarchical scheduling approaches, that could identify code fragments and schedule them optimally. Consequently deal with manageable code size that don't reach these exact methods limits.

# **1.6** Contributions

This thesis presents some solutions to the resource-constrained scheduling problems for HLS. Indeed, for efficiently scheduling programs, especially with loops, first, we make easy the problem by organizing the scheduling process in stepwise ways. We propose two approaches: Two-step and Three-step approaches.

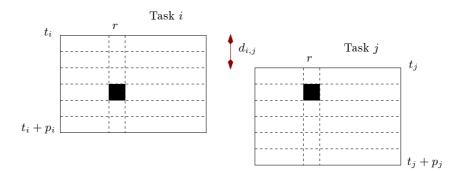

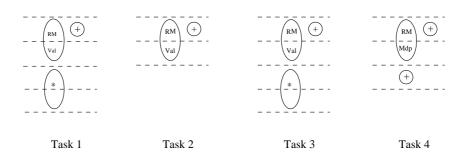

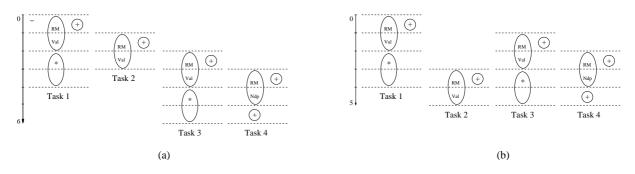

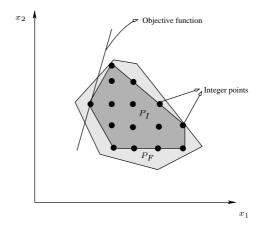

First, a formalism to accurately express resource constraints for complex tasks represented as reservation tables is proposed. Indeed, the resource constraints are modeled by "dis-equations" and finding an optimal schedule entails resolving a system of dis-equations. The proposed formalism can be generalized to support problems of resource-constrained scheduling even when tasks are data-dependent.